# **HPO<sup>™</sup> EDA-Plus Enables An Ultimate DTCO**

Chip making from art to science to intelligence

Zongchang Yu, Shengrui Zhang, Ming Ding, Min Hong and Zhao Chen, etc.

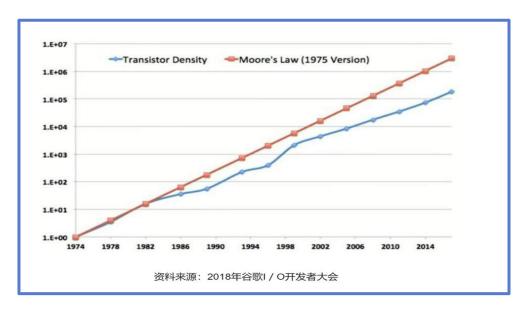

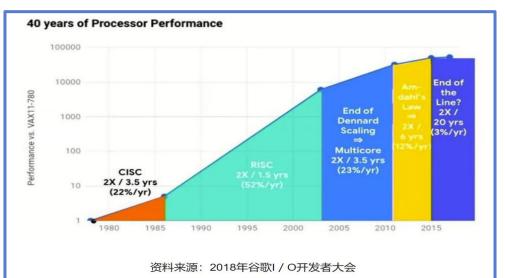

#### **Slowing down in Moore's Law, More than Moore**

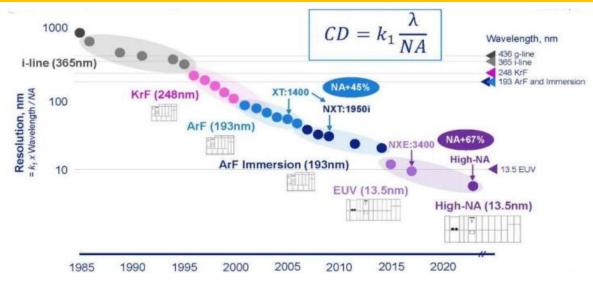

Extending Moore's law by upgrading hardware has hit physical or economic limitations:

- Making of "point tools" has become more challenging.

- IC manufacturing processes have become more and more complicated and expensive .

- The Result: monopoly in IC supply chain, winners take the largest profit.

#### EUV: Only one vendor ! Hardware based Moore's Law is ended. Crisis, but also opportunity for Holistic Process Optimization !

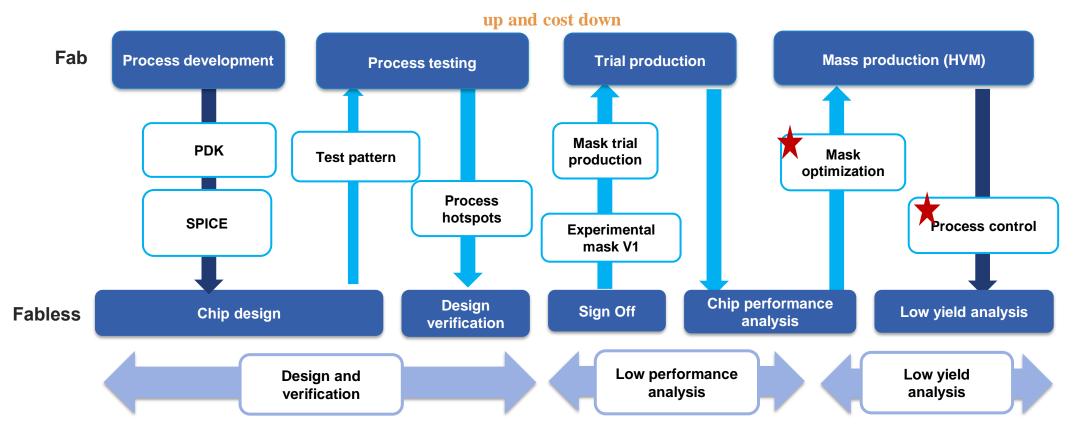

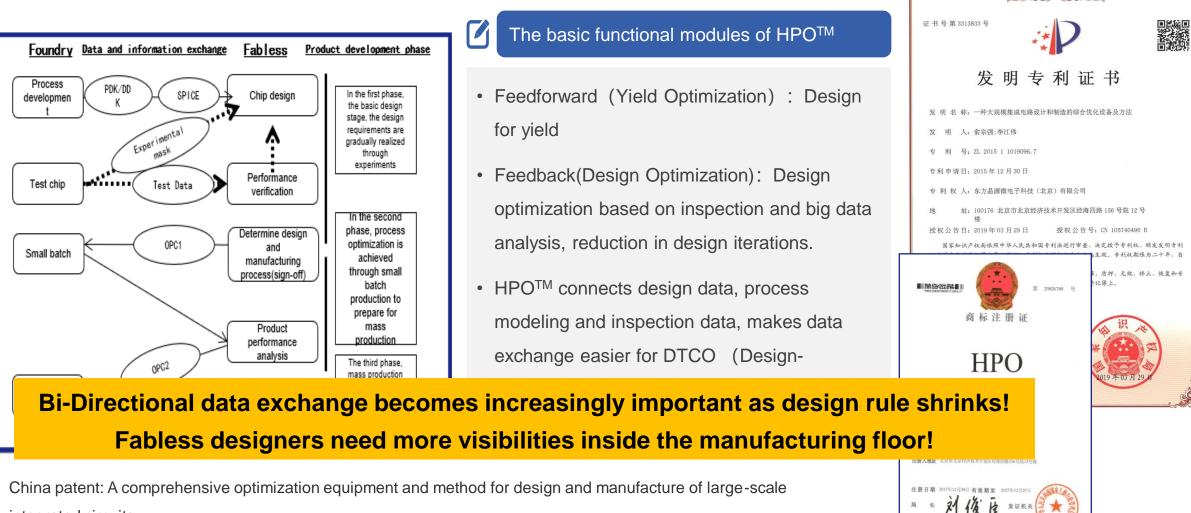

## **Complexity and pain points in design and manufacturing CoOp**

Data sharing and comprehensive optimization of design and manufacturing are the key to shorten R&D cycle and achieve yield

- Complex of processes involving multiple parties

- Amount of data related to process quality reached humongous level beyond capacity of current system

- The PDK no longer accurately and timely represents the manufacturing capacity of a given fab

- Yield is heavily rely on engineers' experiences in both fab and in fabless

#### Yield predictability becomes key factor of shortening R&D cycle

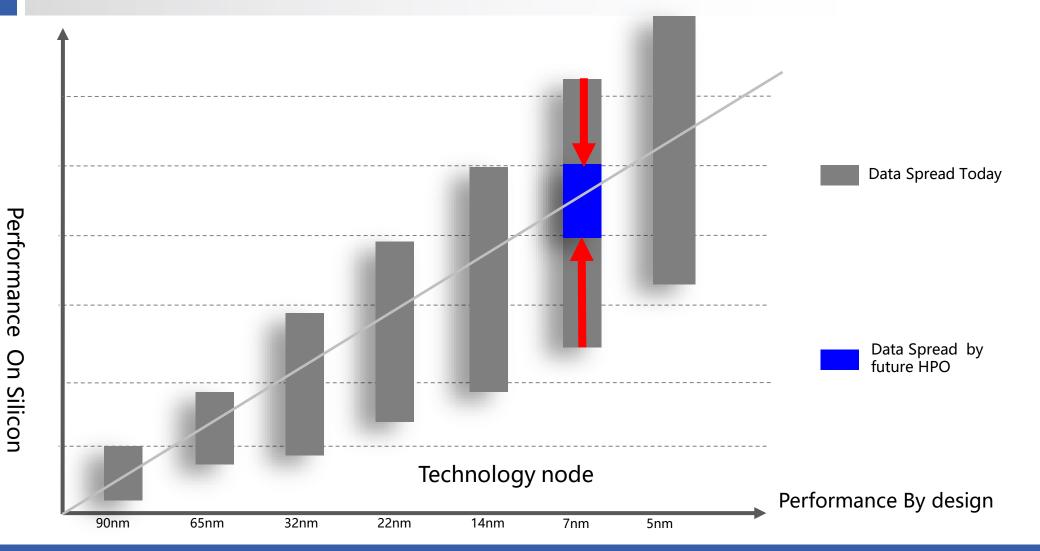

Large spread of measured vs. designed resulting more iterations, longer yield ramping, eventually increasing chip cost and time-to-market.

Also small spread means possibility for less matured tech node to support better chip performance

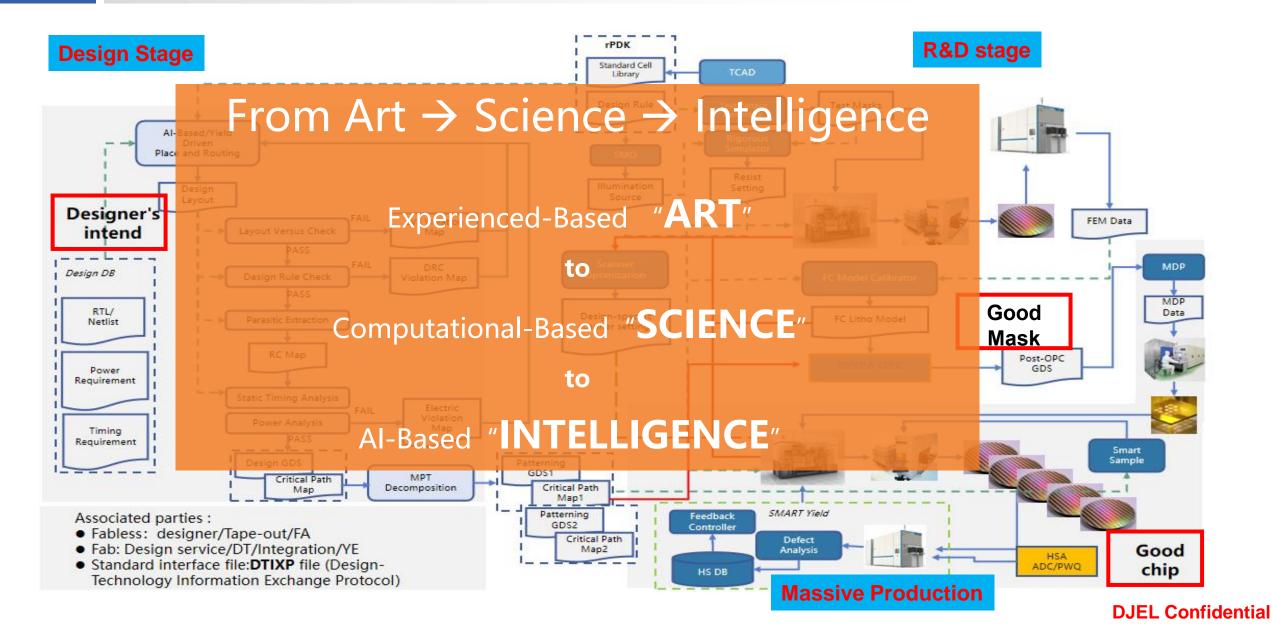

## **Achieving an Al-Based Ultimate DTCO Flow**

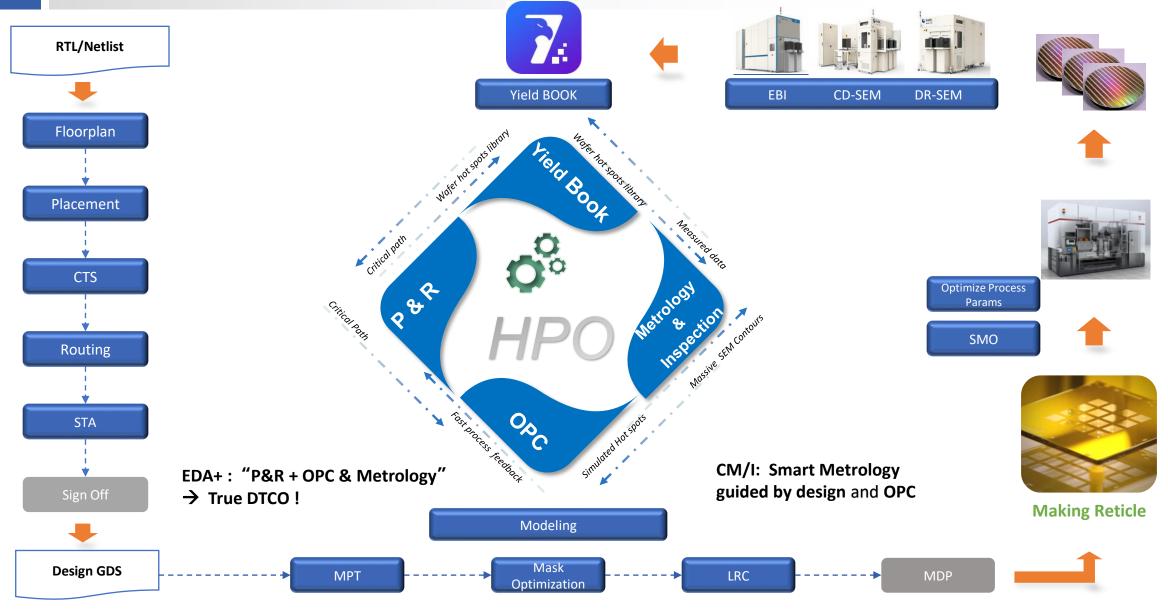

# HPO<sup>™</sup> : Seamless connection between design and manufacturing, platform for an ultimate DTCO

integrated circuits,

Application Number: CN201511019096.7, Application date: 2015.12.30, Priority date: 2014.12.31

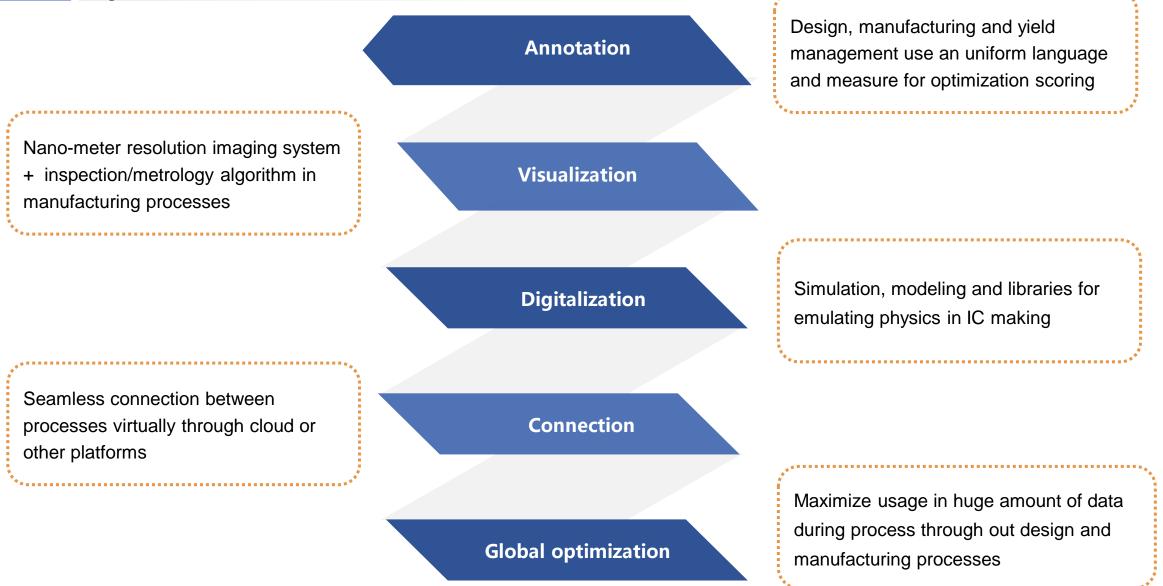

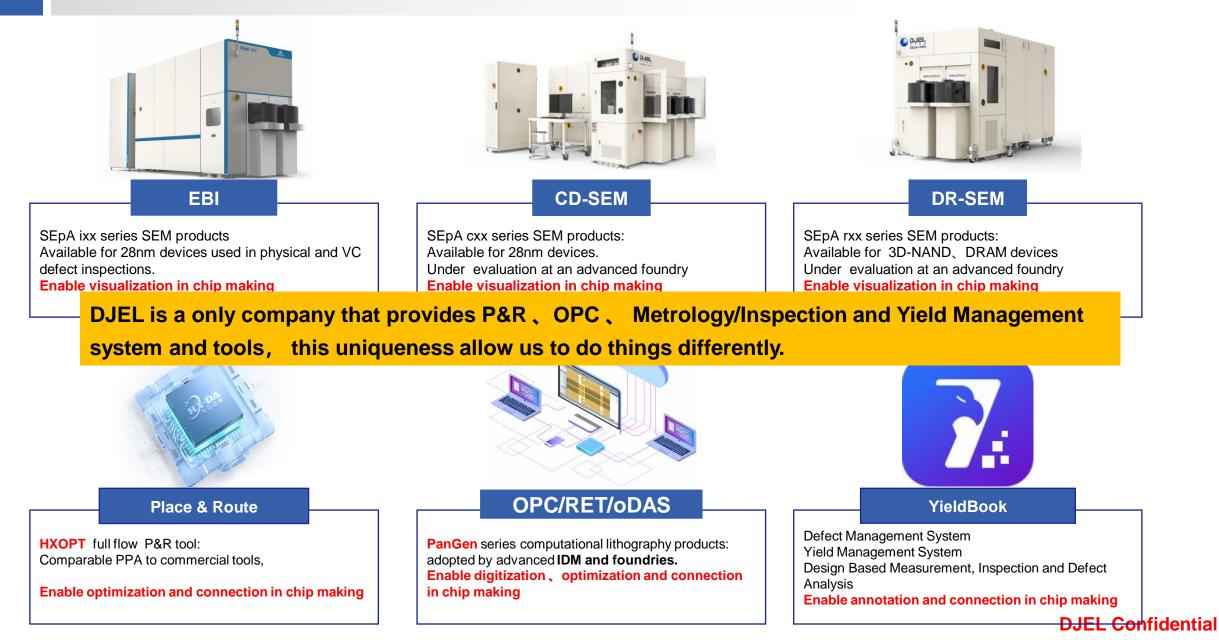

# Key Components: Making yield computable, visible, measurable, globally optimal

#### **Foundation and tools for establishing the HPO<sup>™</sup> Platform**

#### Holistic Process Optimization: EDA-Plus & CM/I

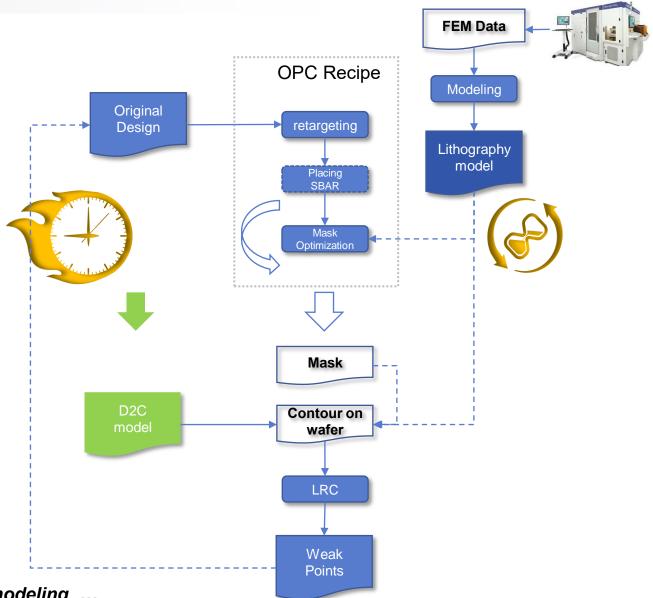

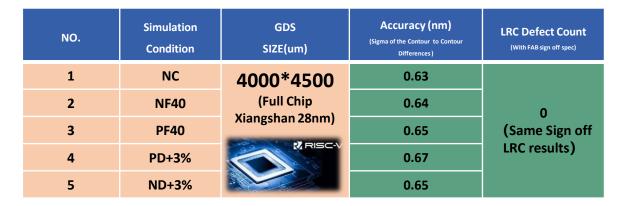

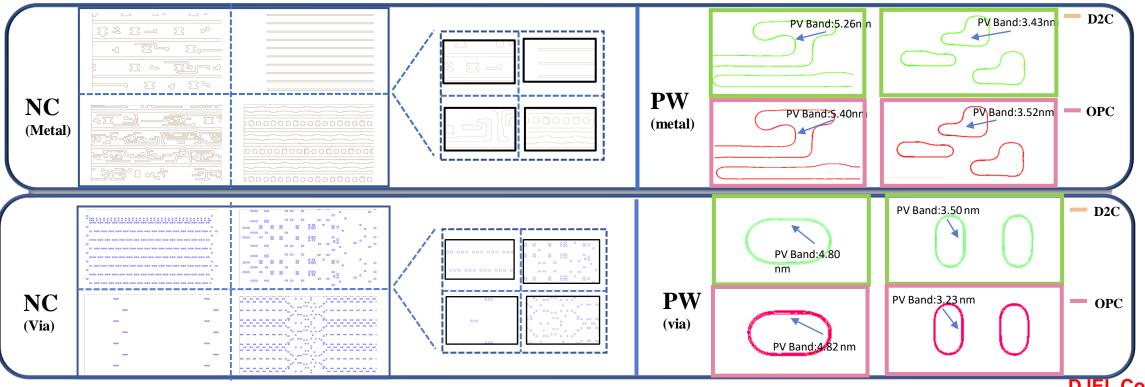

# **D2C:** Fast Feedback From Process to Designer

- Obtain accurate ADI contour from original design

- Fast and direct lithography feedback to designer

- Seamlessly integrated with PanGen OPC Platform

- D2C AI model can be directly calibrated based on PanGen full chip OPC solution

Note: D2C can further extend to etch modeling and HotSpot modeling ...

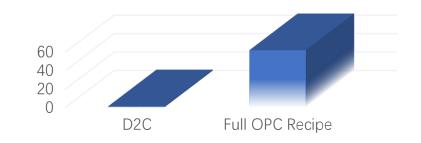

#### **Accurate and Fast Lithography Feedback**

~ 1/60 RUN TIME

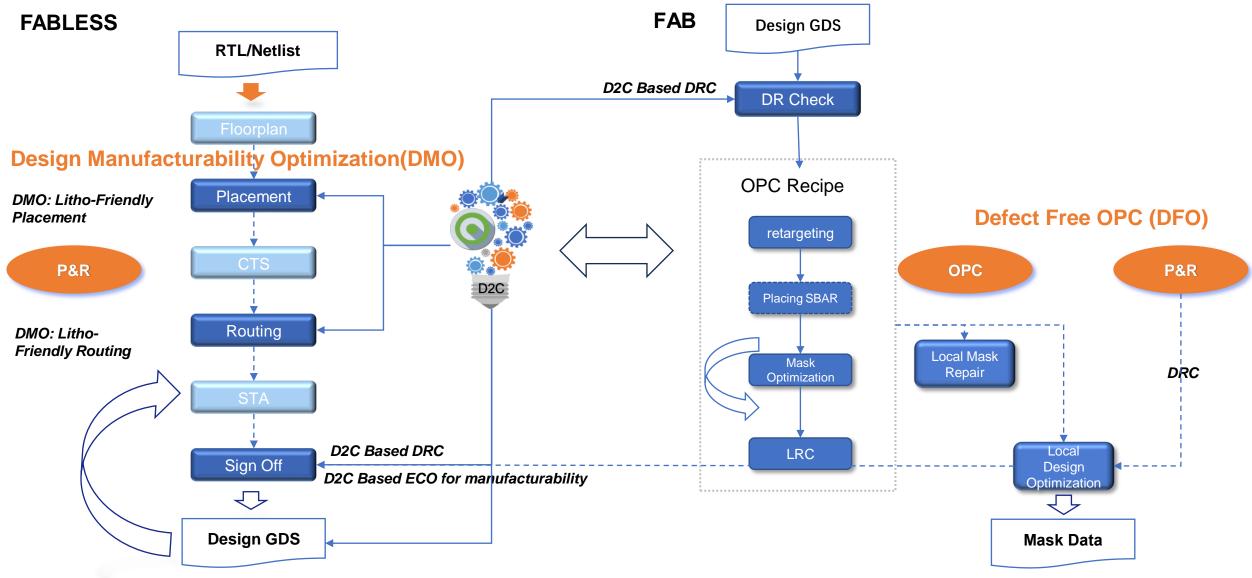

# **HPO<sup>™</sup> EDA-Plus:** From DMO, DFO to TAR

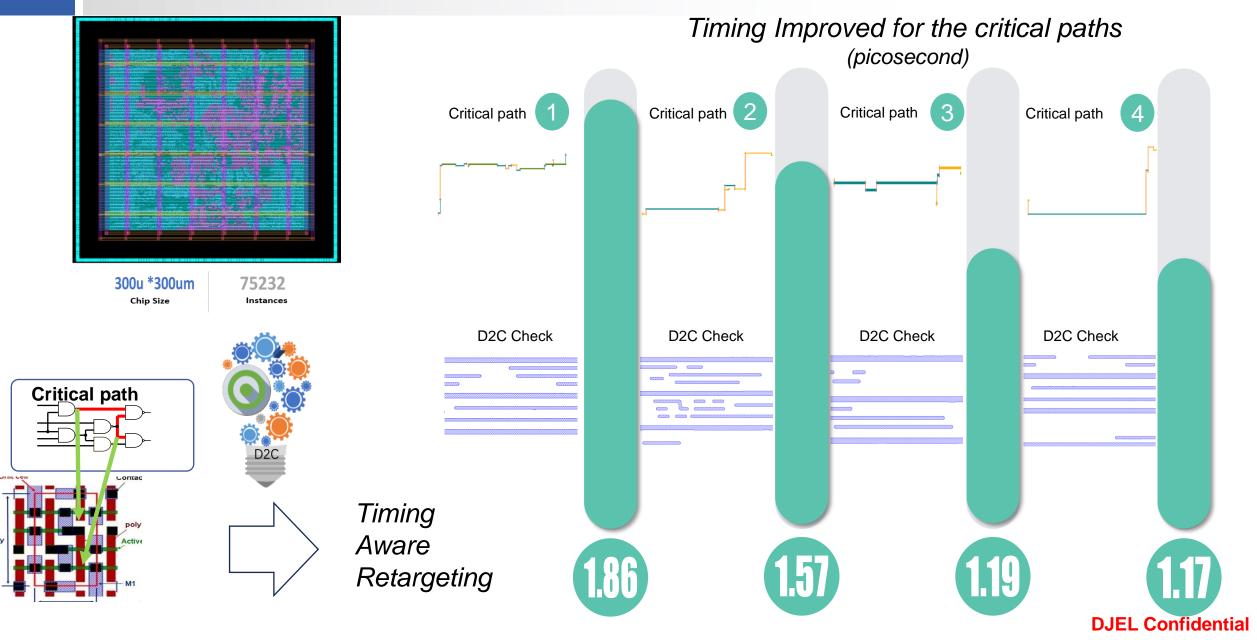

**Timing Aware Retargeting (TAR)**

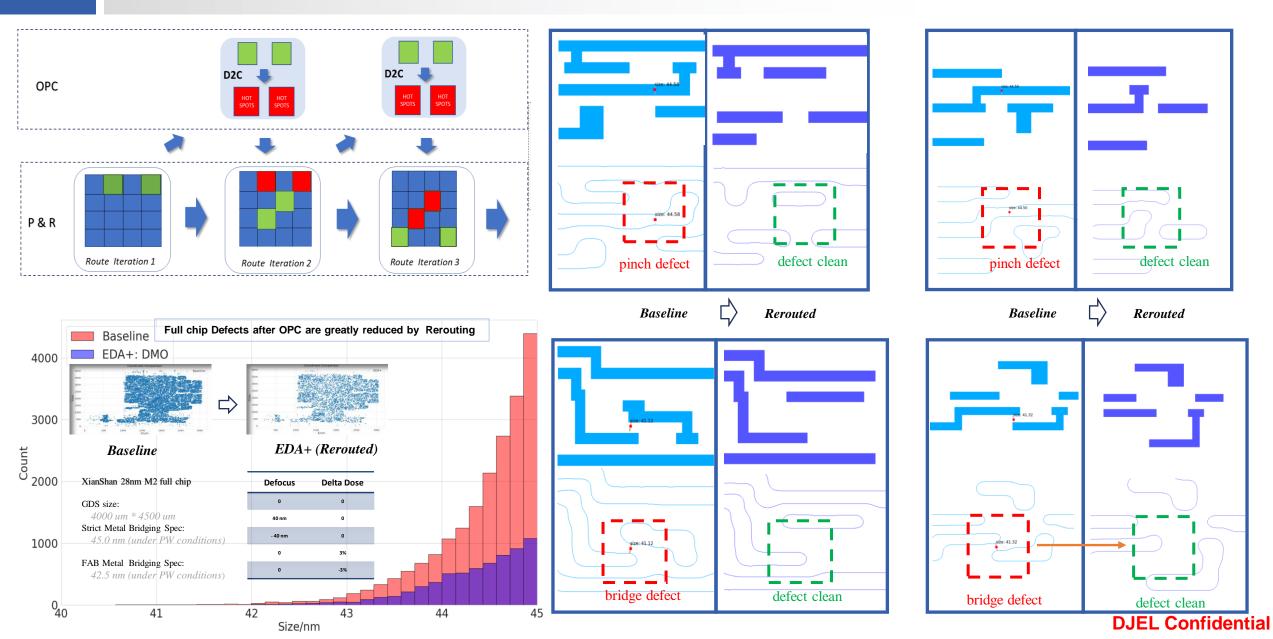

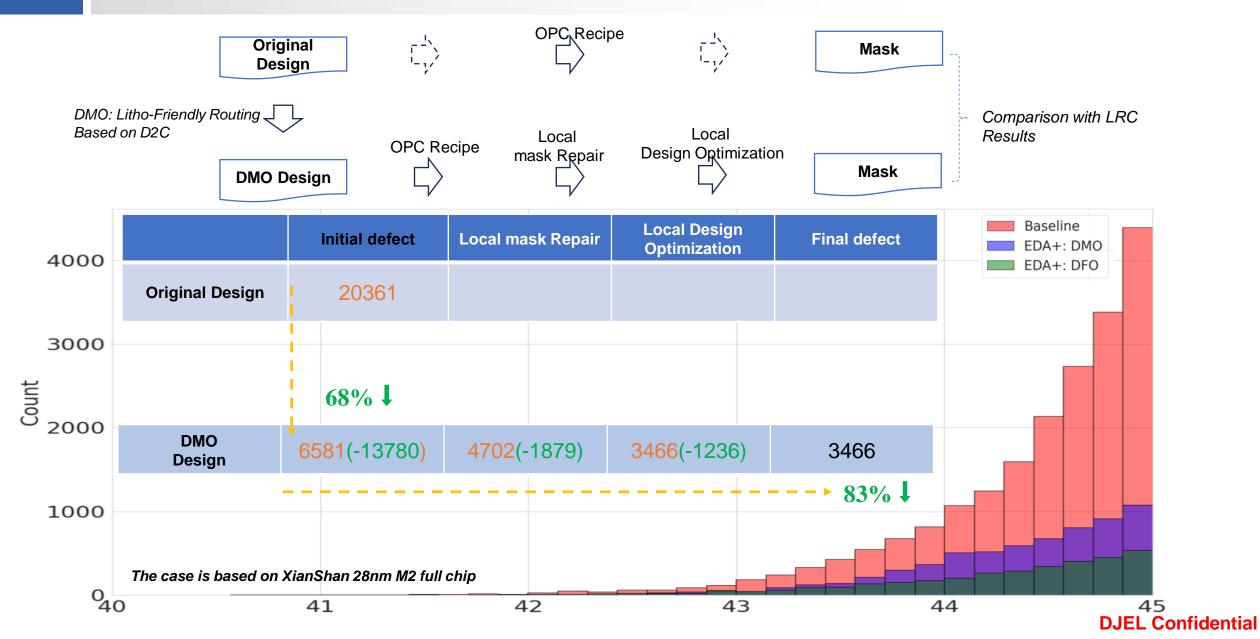

## **HPO<sup>™</sup> EDA-Plus improves the Yield**

## **HPO<sup>™</sup> EDA-Plus improves the Yield cont**

#### **HPO<sup>™</sup> EDA-Plus improves the chip performance**

## **HPO<sup>™</sup> EDA-Plus: Designer's Intend To Good Chip (D2GC)**

- Slowing down of Moore's law provided opportunities for innovation in advanced IC

Making

- □ HPO<sup>TM</sup> EDA-Plus platform enables seamless connection between design and manufacturing to achieve ultimate DTCO, and Al-Based Chip Making

- □ HPO<sup>™</sup> EDA-Plus has show promising results in improving yield and chip performance

- □ We will continue our efforts to add more tools in HPO<sup>™</sup> EDA-Plus system, finally build an innovative infrastructure for Yield up & Cost Down in IC making

# THANKS ALL

东方晶源微电子科技(北京)股份有限公司 DONGFANG JINGYUAN ELECTRON CO., LTD.