## Control Strategy for Improved After-Etch Overlay at Wafer Edge of DRAM Layers in High-Volume Manufacturing

Junjun Zhang1, Jimmy Chang1, Charlie Huang1, Wei Zhang1, Helei Sun1, Xiaofang Zhou1, Bing Wang2, Fan Huang2, Hao Jing2, Justin Jiang2, Matthijs van Reeuwijk3, Maja Vidojkovic3, Hua Li3

> Presenter: Helei Sun 2022/9/28

1CXMT (ChangXin Memory Technologies, Inc.), No. 388, Xingye Avenue, Economic and Technological Development Area, Hefei, China 2ASML China, Innovation Avenue, High-Tech Area, Hefei, China 3ASML Netherlands, P.O. Box 324, 5500 AH, Veldhoven, Netherlands

### **H** Background introduction

Benefit of control strategy (scenarios & simulations)

Conclusion

🙎 Q & A

### **H** Background introduction

Benefit of control strategy (scenarios & simulations)

Conclusion

**Q&A**

## **Background introduction**

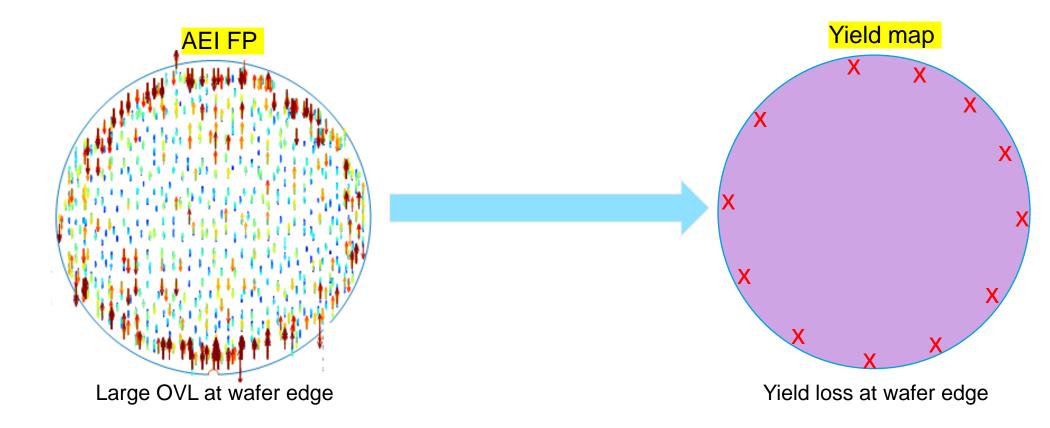

• CXMT sees severe edge AEI OVL can often lead to edge yield loss

#### **H** IDM & ASR introduction

### Benefit of control strategy (scenarios & simulations)

Conclusion

🙎 Q & A

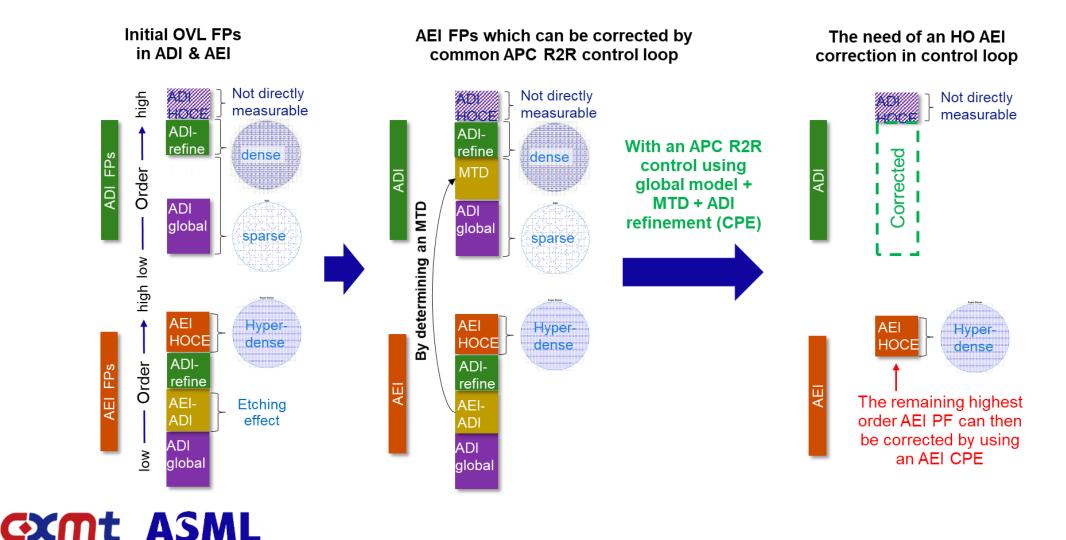

# Overlay components in ADI and AEI, and their corrections in control loop

• Conventional APC control loop needs to be extended to cover high-order AEI fingerprint

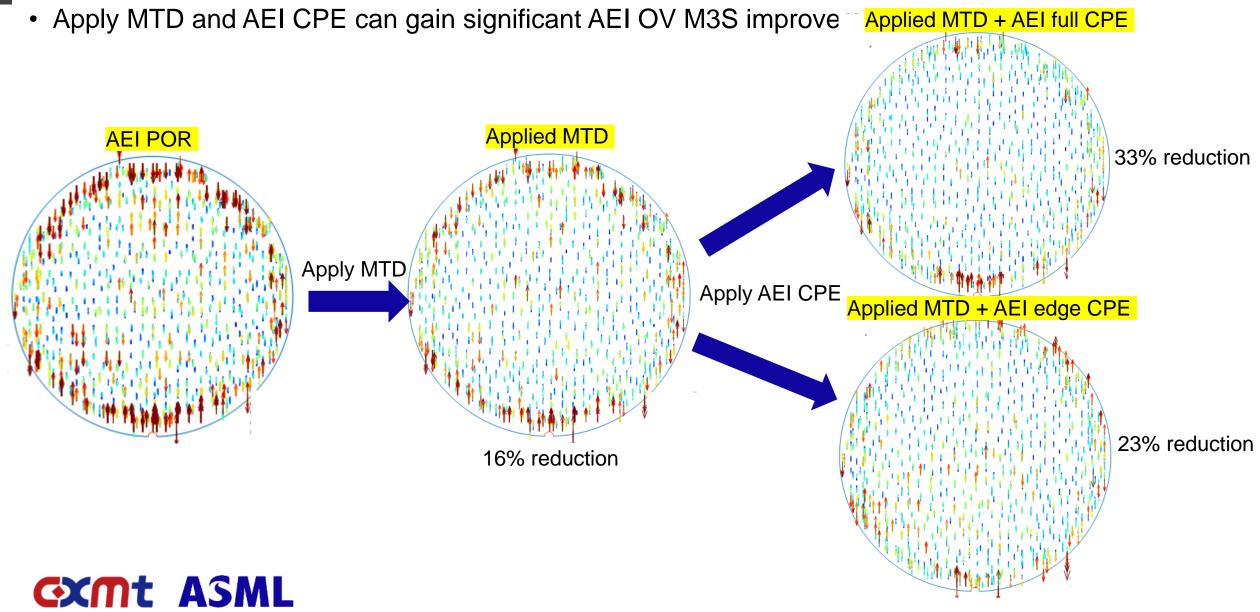

## Global MTD + AEI CPE simulations

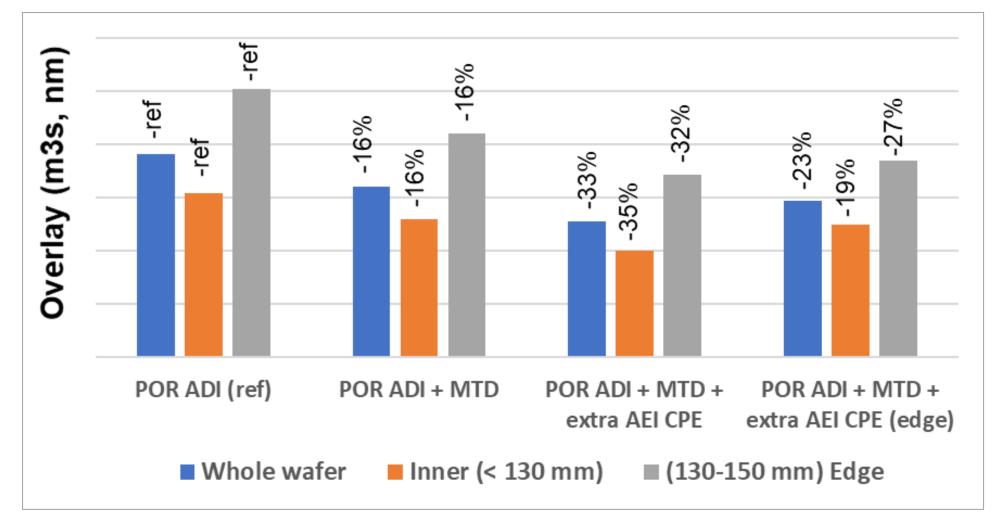

## AEI OPO gains by different control scenarios

• Gain at edge vs inner: about similar % for both, but much larger in term of nm for edge

### **H** IDM & ASR introduction

Benefit of control strategy (scenarios & simulations)

O Conclusion

**Q & A**

## Conclusions

- Critical DRAM layers could suffer from larger after-etch overlay at wafer edge area. A common

practice of adding a global MTD is helpful, but it may not be enough for edge area due to high order

nature of the FP there.

- By adding an extra AEI CPE on top of control loops of ADI APC and MTD in several scenarios, we showed that this approach is very effective in reducing AEI overlay of the addressed layer for full wafer and especially for the edge area.

- By this way, we expect higher yield can be achieved for critical DRAM layers, especially at wafer edge area.

### **◄** IDM & ASR introduction

Benefit of control strategy (scenarios & simulations)

Conclusion

🙎 Q & A